Details

Description

Feature Summary

By the end of PI16, the goal of this Pulsar Timing Epic is to create a functional voltage recorder controlled via CSP.LMC, capable of recording the tied-array voltages from the PST CBF, with limited sample length and/or bandwidth flexibility.

Detailed Description

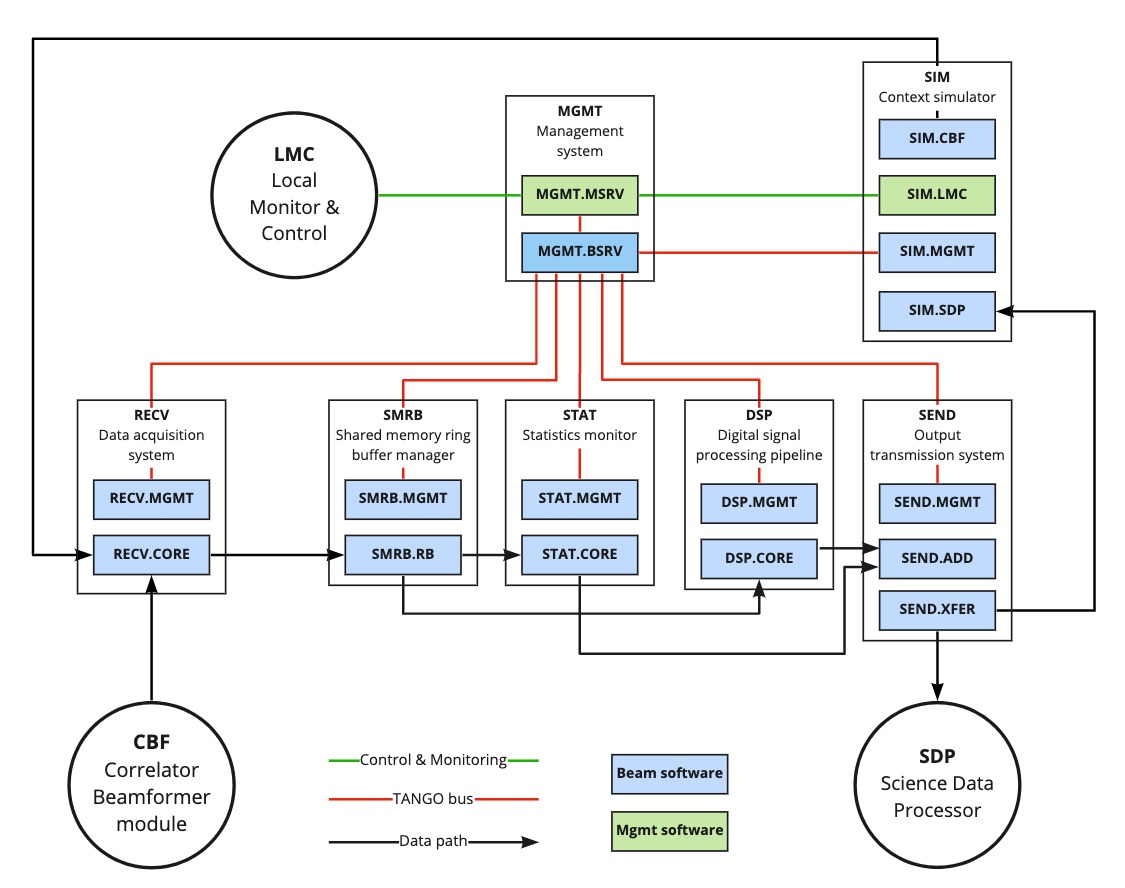

PST Voltage recorder to enable verification of the CBF channeliser and beamformer, PST will be capable of recording the tied-array voltages. The recording will be limited in duration (e.g. 30 seconds) or bandwidth (e.g. 100 MHz) and will use a system composed of partially-completed versions of the following additional PST components:

Shared memory ring buffer (SMRB):

- SMRB.RB: circular ring buffer in CPU RAM used to store data at limited acquisition rates

- SMRB.RB.WB: store meta-data streams in ring buffer

- SMRB.RB.DB: store data streams in ring buffer

Data acquisition (RECV):

- RECV.CORE.UDP: Receive interface for CBF PSR packet format at limited acquisition rates

- RECV.CORE.CTRL: Report interface capture rates, interface errors and capture packets and write tied-array voltage data to SMRB

Flow Through Mode (DSP):

- DSP.DADA: reads voltage data from SMRB and writes to local disks in an internal engineering format (PSRDada files). Perform no renormalisation or re-quantisation

Common Software (COMM):

- COMM.MGMT: TANGO base classes specific to PST

- COMM.K8S: Kubernetes deployment frameworks

- COMM.CTRL: C++ control and monitoring library

Management (MGMT):

- RECV.MGMT: TANGO device for RECV

- SMRB.MGMT: TANGO device for SMRB

- DSP.MGMT: TANGO device for DSP